Current version: 1.0 – First Release!

Introduction:

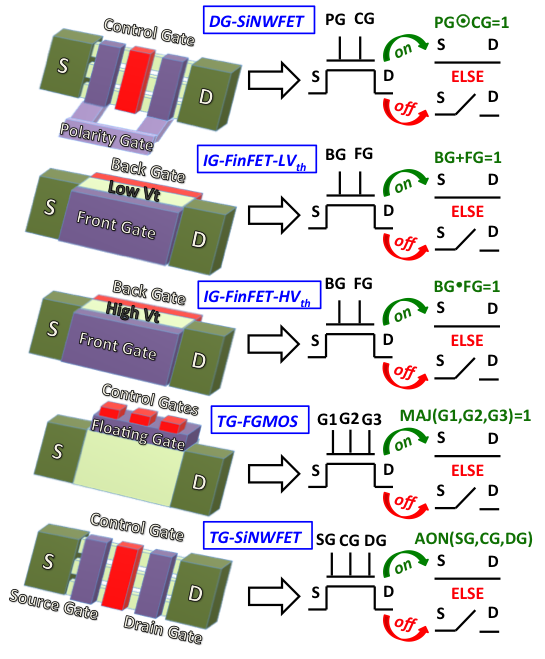

The use of Multiple Independent Gate Field Effect Transistors (MIGFETs) is a promising scaling path for digital electronics [1]. Originally introduced to achieve a better electrostatic control over a FET channel [2], [3], MIGFETs have recently demonstrated the ability to enclose complex switching functions into a single device [4]–[8]. From a design perspective, enhancing the functionality of elementary components opens up new efficient logic implementations. For example, MIGFETs in [4] realize fast datapath circuits [9] as they switch based on the XNOR operation between gate signals. Analogously, MIGFETs in [6] enable compact control logic circuits as they switch based on the AND/OR between gate signals. Other MIGFETs with expressive switching functions, e.g., gamble [5] and threshold [8] functions, advantageously fit other classes of circuits.

While a MIGFET functionality increases with the number of gates, also its physical implementation cost grows. Researchers face then the question: How many gates do we need?

We developed a MIGFET logic synthesis tool to answer the logic side of this question.

MIGFET Synthesis tool:

The MIGFET synthesis package consists of about 3k lines of C code. It also includes the BBDD package [9] to perform logic manipulation/optimization tasks efficienctly. The input to the software are:

- Circuit file description in BLIF format, premapped into k-LUTs

- Technology file with basic device characteristics

- Switching function of the target MIGFET in BLIF format

Based on these data, the software estimates area, delay, energy and power metrics for the input circuit implemented by an optimized set of pseudo-logic cells. The logic core of the MIGFET software performs dedicated optimization to fully harness a MIGFET functionality (pivotal asset). More details about the logic synthesis methodology employed are reported in [10]. Also interconnect models (Rent’s rule and Donath’s rule) are embedded in the MIGFET estimation engine. The output of the software is a netlist of gates with detailed area/delay/energy informations.

Typical compilation/execution flow:

By typing help in the command line interface all execution options (and short-names) are listed.

Download MIGFET package:

Please click here to download.

Contact:

Please contact me for any questions you might have about the MIGFET package, at luca dot amaru at epfl dot ch. I am also happy to provide help in using/customizing the options for your intended application of the package.

Related publications:

[1] ITRS available online at http://www.itrs.net.

[2] J.-P. Colinge, FinFETs and Other Multi-Gate Transistors,. Springer US,

2008. 1-48.

[3] S. Cristolovenau, How Many Gates Do We need in a Transistor?,

International IEEE Semiconductor Conference, 2007. CAS 2007.

[4] M. De Marchi, et al. Polarity control in double-gate, gate-all-around

vertically stacked silicon nanowire FETs, Proc. IEDM, 2012.

[5] J. Zhang, P.-E. Gaillardon, G. De Micheli, Dual-threshold-voltage config- urable circuits with three-independent-gate silicon nanowire FETs, Proc.

ISCAS, 2013.

[6] M. Rostami, K. Mohanram, Novel dual-V th independent-gate FinFET

circuits, Proc. ASPDAC, 2010.

[7] O. Takahide, et al. A majority-logic device using an irreversible single-electron box, IEEE Transactions on Nanotechnology, 15-22, 2003.

[8] T. Shibata, T. Ohmi, A functional MOS transistor featuring gate-level weighted sum and threshold operations, IEEE Transactions on Electron Devices, 39.6 (1992): 1444-1455.

[9] BBDD Package: http://www.epfl.ch/labs/lsi/BBDD

[10] L. Amarù, G. Hills, P.-E. Gaillardon, S. Mitra, G. De Micheli, “Multiple Independent Gate FETs: How Many Gates Do We Need?”, Asia and South Pacific Design Automation Conference (ASP-DAC 2015), Chiba/Tokyo, Japan, 2015.