Thesis title: New Data Structures and Algorithms for Logic Synthesis and Verification

Year: 2015

Electronic Design Automation for Emerging Technologies and Applications

Contacts:

Luca Amar, PhD student, EPFL-IC-LSI

Pierre-Emmanuel Gaillardon, Post-doc, EPFL-IC-LSI

Giovanni De Micheli, Professor, EPFL-IC-LSI

Presentation:

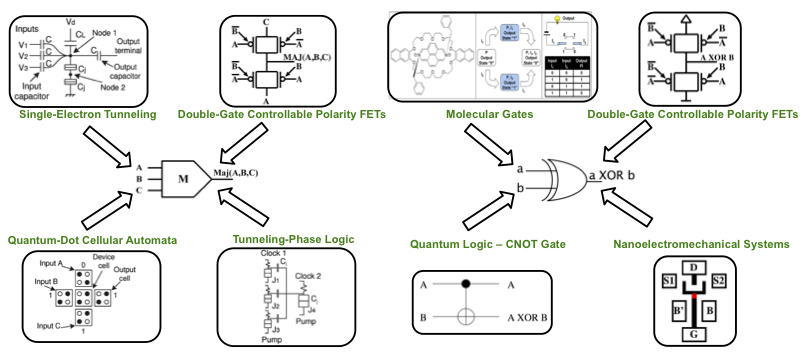

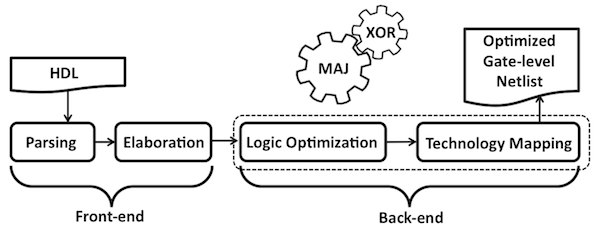

In the last half-century, automated logic design has been crucial to enable the exponential growth of digital circuits complexity predicted by Gordon Moore in 1965. Nowadays, the relentless evolution of electronics is threatened by physical limitations of conventional CMOS technology to further scale down transistor size. To sustain Moore’s prediction in the future, researchers are focusing their attention on emerging nanotechnologies as candidates for replacing traditional CMOS. However, nanotechnologies often carry different logic primitives, for example majority and XOR, for which contemporary logic synthesis techniques are not fully satisfactory.

As progress is made in beyond CMOS devices, research must be also conducted in automated synthesis flows to fully exploit the logic expressive power led by new technologies.

Additionally, the study of novel synthesis techniques, exploiting different Boolean primitives, is also interesting for standard designs and technologies. Indeed, new approaches can push further the efficacy of logic synthesis for conventionally hard-to-synthesize circuits, rich, for example, in arithmetic functions.

Last, but not least, there is a trend to use EDA algorithms in non-traditional EDA fields (e.g., data compression, cryptography, medicine, smart-grid, etc.) where logic synthesis can solve important problems.

Goals:

The goal of this project is to develop innovative synthesis methodologies aiming to (i) unlock the expressive power of emerging technologies based on new Boolean primitives (ii) bridge the quality gap between automatically designed random/control logic and data-paths (iii) extend the use of logic synthesis to non-traditional EDA applications.

Main publications:

L. Amaru, P.-E. Gaillardon, G. De Micheli ,”An Efficient Manipulation Package for Biconditional Binary Decision Diagrams“, Design, Automation & Test in Europe Conference (DATE 2014), Dresden, Germany, 2014.

P.-E. Gaillardon, L. Amaru, J. Zhang, G. De Micheli, “Avanced System on a Chip Design Based on Controllable-Polarity FETs“, Invited, Design, Automation & Test in Europe Conference (DATE 2014), Dresden, Germany, 2014.

L. Amaru, P.-E. Gaillardon, A. Burg, G. De Micheli, “Data Compression via Logic Synthesis“, Asia and South Pacific Design Automation Conference (ASP-DAC 2014), Singapore, 2014

L. Amaru, P.-E. Gaillardon, J.Zhang, G. De Micheli, “Power-Gated Differential Logic Style Based on Double-Gate Controllable Polarity Transistors“, IEEE Transactions on Circuits and Systems II: Express Briefs (TCAS-II), accepted for publication, 2013.

P.-E. Gaillardon, L. Amaru, S. Bobba, M. De Marchi, D. Sacchetto, Y. Leblebici, “Nanosystems: Technology and Design“, G. De Micheli, Invited, Philosophical Transactions of the Royal Society of London. A, 2013.

L. Amaru, P.-E. Gaillardon, G. De Micheli, “Efficient Arithmetic Logic Gates Using Double-Gate Silicon Nanowire FETs“, Invited, 11th IEEE NEWCAS Conference (NEWCAS 2013), Paris, France, 2013

P.-E. Gaillardon, M. De Marchi, L. Amaru, S. Bobba, D. Sacchetto, Y. Leblebici, G. De Micheli, “Towards Structured ASICs Using Polarity-Tunable SiNW Transistors“, Invited, 50th Design Automation Conference (DAC 2013), Austin, Texas (USA), 2013.

L. Amaru, P.-E. Gaillardon, G. De Micheli, “BDS-MAJ: A BDD-based Logic Synthesis Tool Exploiting Majority Logic Decomposition“, 50th Design Automation Conference (DAC 2013), Austin, Texas (USA), 2013.

L. Amaru, P.-E. Gaillardon, G. De Micheli, “Biconditional BDD: A Novel BDD Enabling Efficient Direct Mapping of DG Controllable Polarity FETs“, Functionality-Enhanced Devices Workshop (FED 2013), Lausanne, Switzerland, 2013.

O. Turkyilmaz, F. Clermidy, L. Amaru, P.-E. Gaillardon, G. De Micheli, “Self-Checking Ripple-Carry Adder with Ambipolar Silicon Nanowire FET“, IEEE International Symposium on Circuits and Systems (ISCAS 2013), Beijing, China, 2013.

L. Amaru, P.-E. Gaillardon, G. De Micheli, “Logic Synthesis for Emerging Technologies“, FETCH Conference (FETCH 2013), poster session, Leysin, Switzerland, 2013, best thesis presentation award.

P.-E. Gaillardon, L. Amaru, S. Bobba, M. De Marchi, D. Sacchetto, Y. Leblebici, G. De Micheli, “Vertically Stacked Double Gate Nanowires FETs with Controllable Polarity: From Devices to Regular ASICs“, Invited, Design, Automation & Test in Europe Conference (DATE 2013), Grenoble, France, 2013.

L. Amaru, P.-E. Gaillardon, G. De Micheli, “Biconditional BDD: A Novel Canonical BDD for Logic Synthesis targeting XOR-rich Functions“, Design, Automation & Test in Europe Conference (DATE 2013), Grenoble, France, 2013.

L. Amaru, P.-E. Gaillardon, G. De Micheli, “MIXSyn: An Efficient Logic Synthesis Methodology for Mixed XOR-AND/OR Dominated Circuits“, Asia and South Pacific Design Automation Conference (ASP-DAC 2013), Yokohama, Japan, 2013, best paper award nomination.

Patents:

L. Amaru, P.-E. Gaillardon, G. De Micheli, “Controllable Polarity FET Based Arithmetic and Differential Logic“, EP 12179928.2, 9 August 2012, US 13/960,964 11, 7 August 2013.