Thesis title: Multiple-Independent-Gate Field-Effect Transistors for High Computational Density and Low Power Consumption

Year: 2016

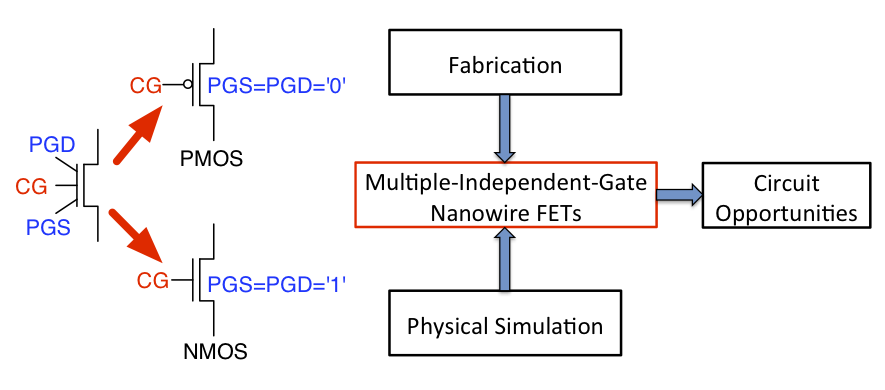

Fabrication and Simulation of Multiple-Independent-Gate Nanowire FETs and Circuits

Contacts:

Jian Zhang, PhD student, EPFL-IC-LSI

Pierre-Emmanuel Gaillardon, Post-doc, EPFL-IC-LSI

Giovanni De Micheli, Professor, EPFL-IC-LSI

Presentation:

While entering into the nanometer regime, planar MOSFETs are suffering from short channel effects and process variations. To overcome these issues, silicon nanowires enable the ultimate electrostatic control of the silicon channel with the gate-all-around structure. Moreover, semiconductor channel with metallic source and drain contacts provides both electron and hole transport in the same device. This gives the opportunity to build dopant-free transistors, whose polarity can be reconfigured by electrostatically controlling the source and drain Schottky barriers.

Polarity-controllable silicon nanowire FETs have been demonstrated with different structures. However, there are still challenges during fabrication, such as the control of Schottky barrier height and the enhancement of drive current, etc. Meanwhile, there are also opportunities to achieve novel applications, such as a dynamic control of the threshold voltage. In addition to the fabrication, physical simulation provides a way to predict the device and circuit performance. The simulation results will help us to understand the physics inside the device and demonstrate novel applications.

Goal:

The goal of this project is to (i) enable a fabrication route for polarity-controllable silicon nanowire FETs and circuits and (ii) provide a simulation flow for the prediction of device and circuit performances.

Publication:

J. Zhang, P.-E. Gaillardon, G. De Micheli, “Dual-Threshold-Voltage Configurable Circuits with Three-Independent-Gate Silicon Nanowire FETs,” International Symposium on Circuits and Systems (ISCAS) 2013.