Architecture Exploration and CAD for RRAM-based FPGA

Contact:

Xifan Tang, PhD Student, EPFL-IC-LSI

Mathias Soeken, Post-doc, EPFL-IC-LSI

Giovanni De Micheli, Professor, EPFL-IC-LSI

Presentation:

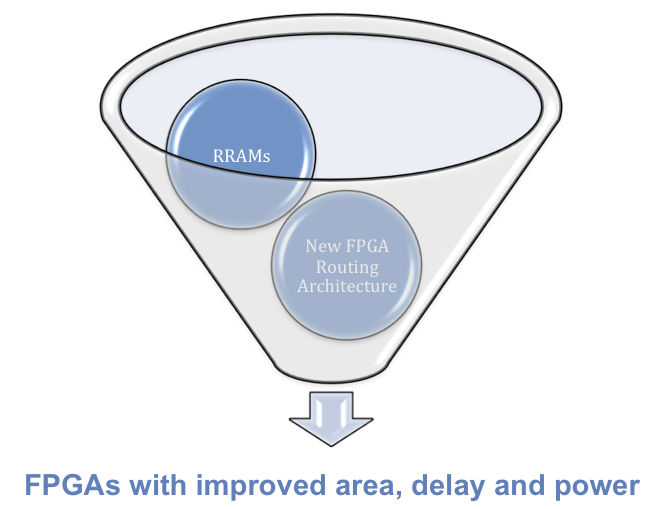

The versatility of Field Programmable Gate Arrays (FPGAs) is accounted to the rich usage of programming switches within the structure. Moreover, they also create large gap between FPGAs and ASICs in area, delay and power. Resistive Random Access Memories (RRAMs) open opportunities in narrowing this gap by replacing Static Random Access Memories (SRAM)-controlled programmable switches with RRAMs exhibiting in low-resistance state. Importing RRAMs into FPGA architecture proposes prospective novel routing architecture and CAD (Computer Aided Design) that attempts to release the full potential of FPGA architecture.

Goals:

- Propose novel FPGA architecture that is appropriate for RRAMs.

- Develop CAD such as logic synthesis, packer, placer and router to co-optimize the novel architecture.