A simulation-based power estimation framework for FPGAs

Introduction:

FPGA-SPICE is a simulation-based tool dedicated to accurate power estimation of Field Programmable Gate Arrays (FPGAs)1.

FPGA-SPICE is an extension to the Verilog-To-Routing (VTR) tool suite2 and is tightly integrated into the Versatile Placement and Routing (VPR) tool.

FPGA-SPICE aims at generating SPICE netlists of a wide range of FPGA architectures, enabling accurate power analysis.

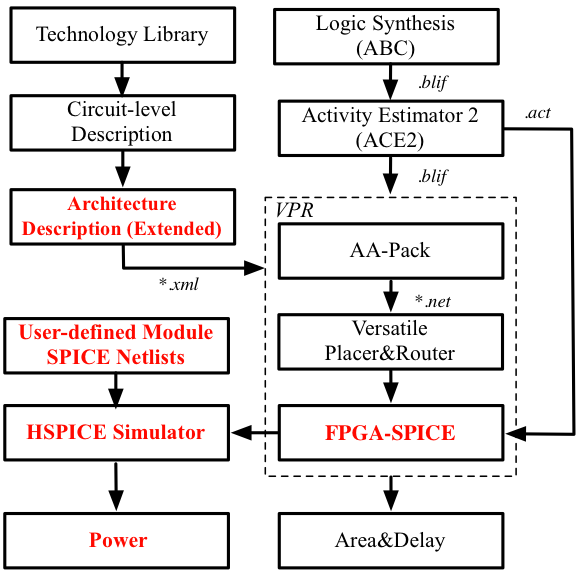

The software flow used by FPGA-SPICE is shown below in Fig. 1.

Fig. 1– Modified VTR flow for FPGA-SPICE

The architectural description language of VPR3 is extended to provide rich transistor-level modeling parameters for FPGA modules.

FPGA-SPICE can automatically generate fine-grain elementary circuits, such as multiplexers and LUTs, but also support user-defined SPICE netlists of FPGA modules.

In order to follow the trend of emerging technologies, FPGA-SPICE also supports innovative architectures, such as RRAM-based circuit designs4.

FPGA-SPICE manages the simulation complexity, by offering three levels of simulations with different simulation time / accuracy tradeoffs.

Download link:

Please click here to download. You will access a short on-line survey; after answering the questions you will be able to download the FPGA-SPICE package.

Contact:

Please contact Mr. Xifan Tang for any questions you might have about FPGA-SPICE, at xifan dot tang at epfl dot ch.

Related publications:

[1] X. Tang et al., FPGA-SPICE: A Simulation-based Power Estimation Framework for FPGAs, ICCD 2015.

[2] J. Rose et al., The VTR Project: Architecture and CAD for FPGAs from Verilog to Routing, FPGA, 2012, pp. 77-86.

[3] J. Luu et al., Architecture Description and Packing for Logic Blocks with Hierarchy, Modes and Complex Interconnect, FPGA, pp. 227-236, 2011.

[4] X. Tang et al., A High-Performance Low-Power Near-Vt RRAM-based FPGA, FPT, pp. 207-214, 2014.