Network-on-chips

NoCs have been proposed as the centerpiece to interconnect the on-chip IP blocks to create efficient, scalable and flexible homogeneous or heterogeneous MPSoCs. Especially in the heterogeneous case, the complex and non-uniform nature of the system resulting network traffic (e.g. video and audio streams, real-time interrupts, message-passing traffic, cache refills and write-backs) and other issues related to dynamic effects generated by the large number of IP cores, i.e. to variations in the operation of the device which occur at runtime, and which are not always easy to predict, makes it essential to provision runtime services at NoC level.

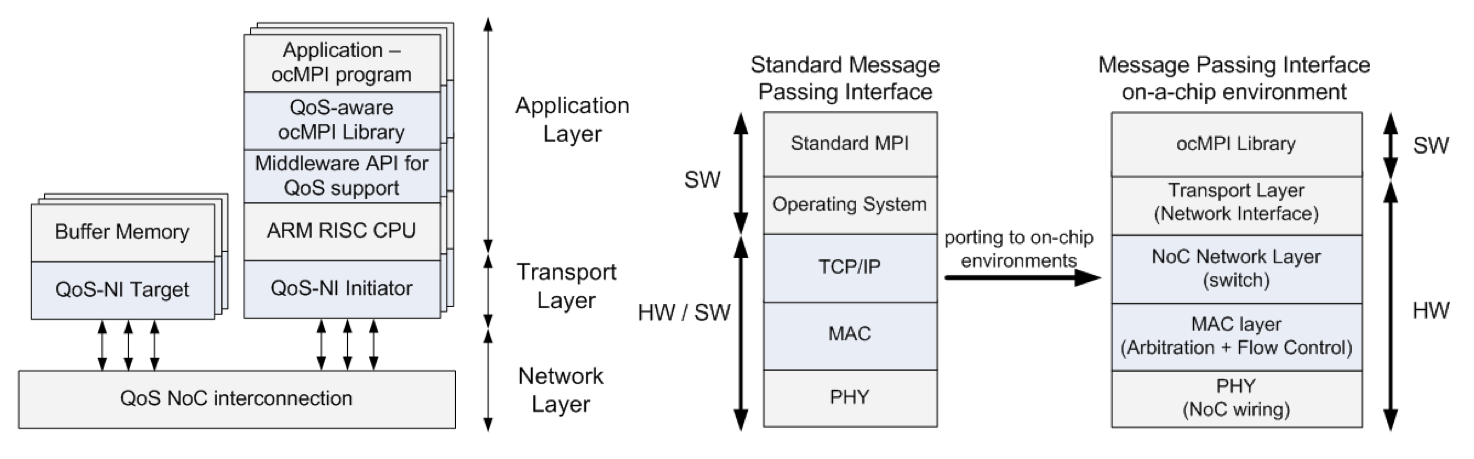

Starting from the architectural level, we plan on building support for the provisioning of services by the NoC to the rest of the MPSoC at runtime, including QoS support and performance monitoring and tuning, dynamic power optimization, as well as debugging facilities including fault detection and handling.

All these services must be made available through software middleware libraries to enable dynamical runtime reconfigurability of NoC characteristics in multi-core systems, as well to provide them on top of parallel programming models. Thus, we will provide a much more efficient design method to deploy IP cores with some degree of flexibility and programmability, and to move implementation details to the software stack that will run on the chip.

Using HW support and SW programmability, jointly with EDA tools will be feasible to achieve optimum behaviour at system-level during the design and execution of applications or use cases on NoC-based MPSoCs, improving performance characterization, and helping the optimization, verification and debugging of complex SoCs.