***Archived: This is a past project, it is not on offer at the moment!***

Project Description:

There are several attempts to use multi-valued logic in computation, storage and interconnections in integrated circuits, since many technological solutions are available and some area saving is expected by using non-binary information. Nevertheless the available designs of the most important parts of the integrated circuits are in binary logic, such as processors and other IPs. Consequently, only certain parts of the circuit can be implemented in n-ary logic, and an interface between n-ary and binary parts of the circuits, which we call binary-to-n-ary decoder, is needed by such hybrid circuits.

In this project we would like to generate – with a binary generator – all possible codes in a given n-ary code space with M digits. Assuming that there are N n-ary codes, we can use a look-up table (LUT) with N entries (rows), ln2N input columns and Mln2n output columns. This table is generally large in size; a better implementation would be to find a logic function implementing the binary-to-n-ary encoding.

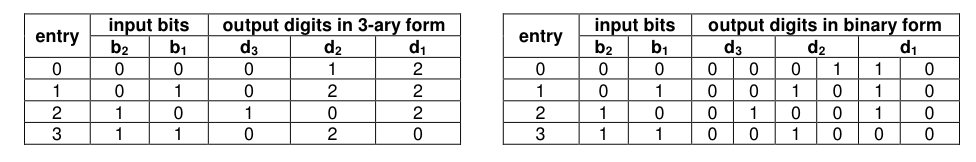

An example is given in the following: Let the basis n be 3, the code space have N=4 codes with M=3 digits each: {012, 022, 102, 020}. The 3-ary ‘0’ is encoded ’00’, ‘1’: ’01’ and ‘2’: ’10’. Then, the LUT reads:

Instead of using this LUT, the output digits can be computed from the input bits; for instance d1,1 = 0 (right most column) and d1,2 = b2 NAND b1 (second column from the right).

Many choices are available to reduce the cost of the multiple-output logic function implementing the LUT, e.g.:

- The order of the entries: the codes are not ordered, we can use the order {012, 102, 020, 022} instead of {012, 022, 102, 020}, etc.

- The binary encoding of the n-ary digits: 3-ary ‘2’ can be encoded as binary ’10’ or ’11’, etc.

The cost of the multiple-valued logic function can be measured in terms of area, power dissipation or latency.

In this project, we consider two given types of n-ary codes that will be explained at the beginning of the project, and a limited number of bases: n takes small values 3, 4, 5… We would like to explore the design space of the binary-to-n-ary decoder for the given codes and the considered values of n, and to generalize the result to any basis n. Exploring the design space consists in estimating area, latency and power dissipation for a set of decoder designs.

Project Organization:

- Literature research on area- and power efficient codes

- Study of the properties of the two n-ary codes (to be explained at the beginning of the project) with respect to area- and power efficient codes

- Formal relationship between entries order and digits encoding from one side and the cost of the binary-to-n-ary decoder from the other side

Requirements:

- Very basic knowledge of encoding

- Basic knowledge of logic synthesis

This project was supervised by Haykel Ben Jamaa.

***Archived: This is a past project, it is not on offer at the moment!***