***Archived: This is a past project, it is not on offer at the moment!***

Project Description:

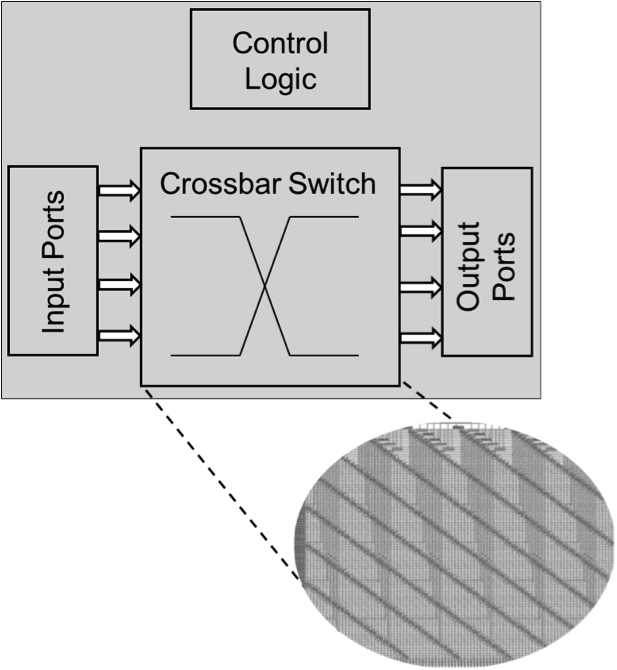

On-chip networks constitute a global interconnection approach for high-performance system-on-chips. The versatility and superior performance of these structured interconnects as compared to traditional bus architectures have been of great interest to the research community. An important component of any on-chip network is the crossbar switch that considerably contributes to the delay and power consumed by the network. This component is part of the network router architecture and is the physical interconnect medium that propagates data packets from an input port (an incoming direction) to an output port (an outgoing direction) as determined be the control logic of the router (see Fig. 1).

Fig. 1. Typical architecture of network router illustrating the layout of a crossbar switch.

Crossbar switches can be custom-designed through careful layout as compared to other physical implementations produced by the synthesis of the corresponding RTL code. The synthesized variants typically consist of serially connected multiplexers that can result in significant area and delay overheads. Alternatively, customized designs can exhibit improved performance characteristics. The purpose of this project, consequently, is to design and optimize a crossbar switch under different design objectives, such as speed, power, and area. The noise margin characteristics of the different designs will also be investigated.

The project will include the following steps: 1) brief literature overview, 2) parameterized modeling the performance of the crossbar switch, 3) design of the crossbar switch (both schematic and layout), and 4) optimization of the design and compare of the model with cadence simulations.

The eligibility requirements for this project are

- VLSI design I and II (EE 431)

- Knowledge of the Cadence tool (schematic entry, virtuoso layout, and analog design environment)

This project was supervised by Dr. Vasilis Pavlidis.

***Archived: This is a past project, it is not on offer at the moment!***