***Archived: This is a past project, it is not on offer at the moment!***

Project Description:

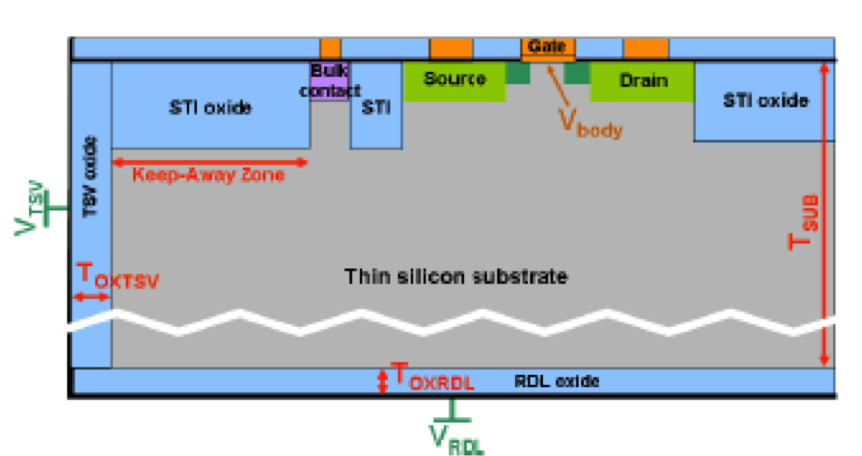

Vertical interconnects – typically implemented with through-silicon or through-oxide vias – are the cornerstone of 3-D integrated circuits. In addition to the manufacturing challenges related to these structures, the interaction of these interconnects with the surrounding circuits has been merely investigated. Preliminary results indicate that in addition to traditional inductive and capacitive coupling among closely placed vertical interconnect, these wires can affect basic characteristics of the transistors, such as the threshold voltage and the mobility. To suppress this interaction keep-out zones around the circuits should be applied in the physical design of 3-D circuits (see Fig. 1). These keep-out zones are expected to appear as additional design rules for the layout of multi-tier circuits.

Fig. 1. Schematic illustration of the cross-section of one tier of a 3-D circuit, where the required keep-out zone to decrease the interaction between a TSV and a nearby transistor is depicted (M. Rousseau, M.-A. Jaud, P. Leduc, A. Francy, and A. Marty, “Impact of substrate coupling induced by 3D-IC architecture on advanced CMOS technology,” Proceedings of the European Microelectronics and Packaging Conference, June 2009.)

Despite these initial results, the interaction mechanism between the TSVs and the transistors is not fully understand and/or described. Consequently, the purpose of this project is to analyze through device level simulators the interplay between vertical interconnect and devices will be explored in depth. Extensive simulations for different interconnect characteristics and integration scenarios will be performed.

The project will include the following steps: 1) understand the basics of the simulation tool (Synopsys, Sentaurus), 2) cover the existing (and rather insufficient) related literature, 2) create the proper simulations structures and scenarios, 3) perform extensive simulations, and 4) analyze the results

The desired qualifications for this project are

- Basic knowledge of semiconductor physics and devices

- Knowledge of the Synopsys, Sentaurus simulator

This project was supervised by Vasilis Pavlidis.

***Archived: This is a past project, it is not on offer at the moment!***