3D NoCs

As technology scaling is predicted to continue towards nano-meter dimensions, more transistors will be available on a single die. However, in order to use these transistors with a limited power budget to achieve the required performance, Systems-on-Chip (SoCs) are evolving into heterogeneous devices that make use of specialized hardware cores (e.g. hardware accelerators, video coding, data encryption) as well as general purpose processors. Interconnecting all these cores in an efficient way is a real challenge. Networks-on-Chips (NoCs) are a promising architecture for an efficient scalable and predictable interconnect. However, tailoring the interconnect network to application specification requires designers to explore huge design spaces.

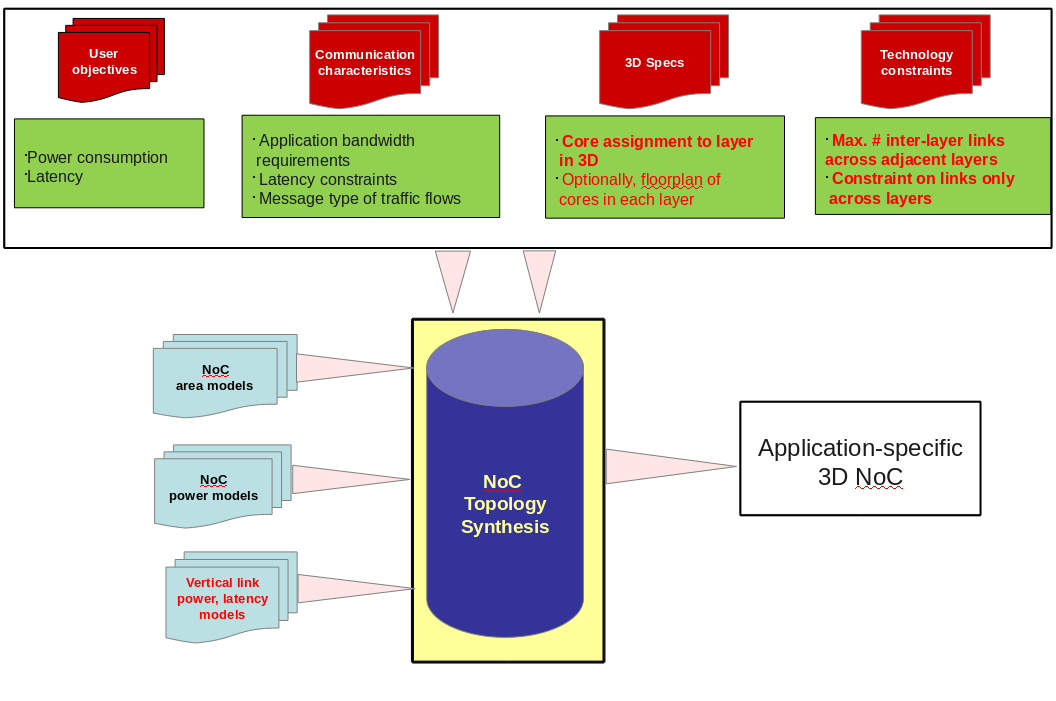

Three Dimensional Integration (3D-IC) is an emerging technology that promises to increase the number of transistors on chip by stacking two or more dies and providing vertical interconnection between the dies. Having vertical interconnections increase the complexity of the design space that needs to be explored when designing the system interconnect. Our goal is to provide tools that can automatically design a custom system interconnect based on application specifications that meets the power/performance requirements and to explore different trade-off solutions.

As wires are scaled along with the transistors, wire delay is increasing when compared to transistor speed. This make synchronous design very complicated and expensive. Most of today’s complex SoC partition the cores in Voltage and Frequency Islands (VFIs) that run at different clock speeds. To reduce the standby power consumption to prolong battery life, unused VFIs should be shutdown. The system interconnect can be the bottleneck that prevents the shutdown of the islands if it is not designed correctly. This further increases the complexity of designing the system interconnect that results in an increased need for efficient design tools. Future extensions, that we want to provide for the tools, include the the design of the NoC towards bottleneck devices (e.g. DRAM controllers), and considering Quality-of-Service during topology synthesis.